Nằm trong chuỗi bài viết hướng dẫn mở rộng bộ nhớ vi điều khiển STM32. Bài viết này sẽ cung cấp các thông tin tổng quan về giao tiếp QSPI, các thông số của QSPI Flash MT25QL128 cũng như hướng dẫn cấu hình ngoại vi QSPI của vi điều khiển STM32 trên giao diện CubeMX.

Các bài viết liên quan nên đọc trước:

IC nhớ FLASH,SDRAM và mô hình bộ nhớ của vi điều khiển khi sử dụng bộ nhớ ngoài

Sử dụng Linker Script trong khai báo, cấu hình sử dụng bộ nhớ ngoài -VĐK STM32

Tổng quan về giao tiếp QSPI

- Giao tiếp QSPI cũng tương tự như giao tiếp SPI nhưng thay vì chỉ có 1 chân truyền, 1 chân nhận dữ liệu thì chúng ta có 4 chân truyền nhận dữ liệu để tăng tốc độ truyền nhận dữ liệu giữa các thiết bị. Giao thức QSPI thường được sử dụng để giao tiếp với bộ nhớ Flash ngoài do tốc độ không đủ đáp ứng để giao tiếp với RAM. Ngoài QSPI, ta còn có OSPI (Octal SPI) là SPI nhưng với 8 chân dữ liệu và cũng thường được sử dụng trong giao tiếp với bộ nhớ Flash ngoài.

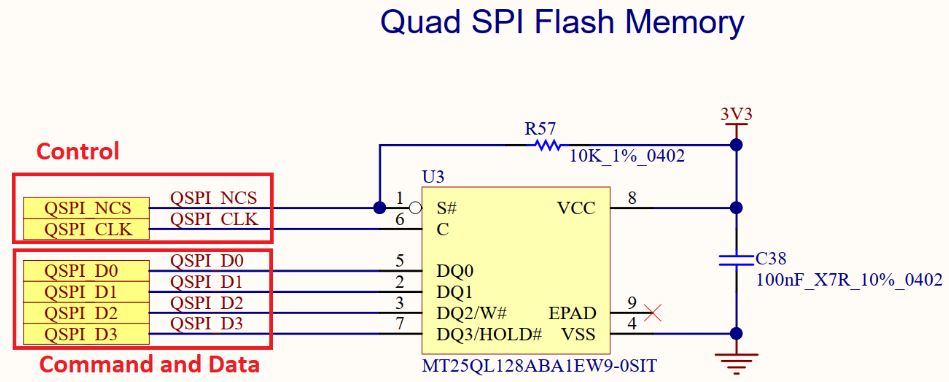

- Giao tiếp QSPI chỉ sử dụng 6 chân tín hiệu như Hình 1 bên dưới:

Hình 1: Chân điều khiển, chân lệnh và data của QSPI Flash

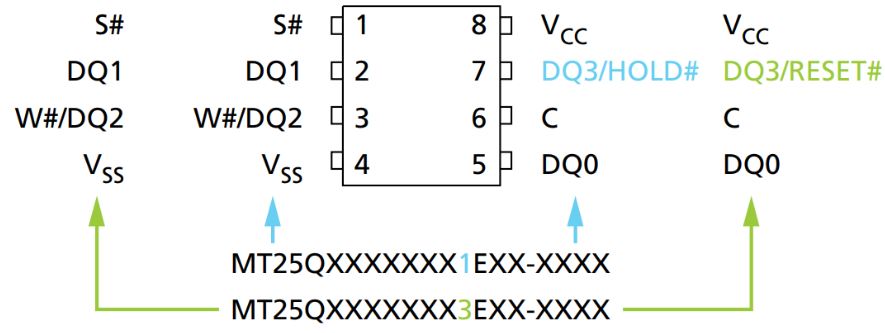

- Các chân Data (D0-D3) còn kèm theo các chức năng khác như W (Write), Hold (đưa các chân Data và Control vào chế độ High Z), truyền địa chỉ và command trước khi thực hiện ghi đọc như Hình 2 bên dưới:

Hình 2: Các chân và chức năng của từng chân trên QSPI Flash

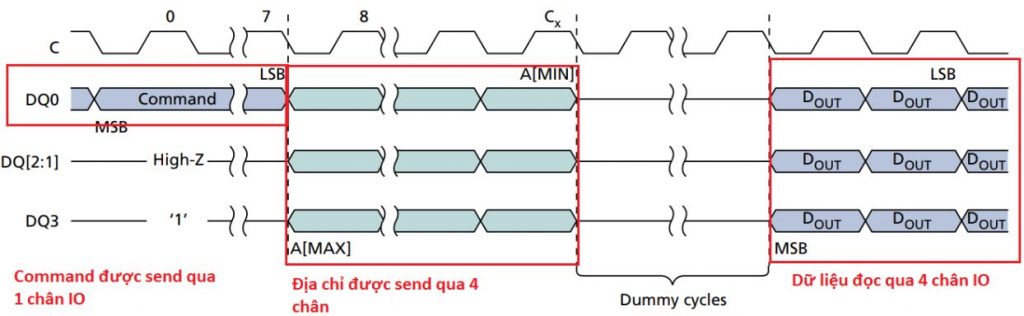

- Như giới thiệu ở các bài viết trước, để đọc/ghi/cấu hình QSPI Flash thì vi điều khiển phải gửi tuần tự lệnh⇒địa chỉ⇒Chờ⇒Dữ liệu như ở Hình 3.

Hình 3: Quá trình đọc dữ liệu QSPI Flash

Các thông số của QSPI Flash

– Trong giao tiếp QSPI, ta cần phải chú ý đến 1 số tham số trong Datasheet để có thể cấu hình chính xác trong STM32CubeMX như Clock, không gian nhớ, Dummy cycles.

– Trong bài hướng dẫn này, tác giả sử dụng board STM32F746-DISCO với bộ nhớ QSPI Flash MT25QL128ABA và để sử dụng ta phải tham khảo datasheet cho chip Flash này [1]. IC nhớ này có các tham số sau:

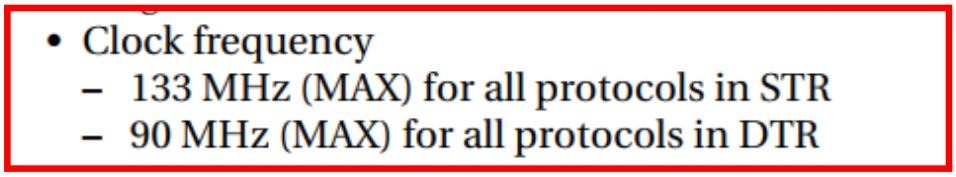

- Tần số hoạt động: 133MHz ở mode STR (Single Transfer Rate); 90MHz ở mode DTR (Double Transfer Rate) như Hình 4.

- STR: nghĩa là ở mỗi xung clock, chip Flash chỉ truyền đi 1 đơn vị dữ liệu (4 bit đối với QSPI)

- DTR: nghĩa là ở mỗi xung clock, chip Flash có thể truyền dữ liệu ở cả sườn lên và sườn xuống của clock (tăng gấp đôi throughput của chip)

- Tuy nhiên, vì việc tận dụng cả 2 sườn nghĩa là dữ liệu ở 2 bên sườn clock phải xuất hiện đúng lúc (vì nếu có cumulative latency – độ trễ tích lũy theo thời gian) thì đến 1 lúc, toàn bộ dữ liệu nhận được sẽ bị sai lệch. Còn nếu chỉ truyền 4 bit / 1 xung clock, thì trong vòng 1 xung clock, ta có thể shift việc đọc dữ liệu trên bus đi ½ chu kỳ để đảm bảo độ toàn tin cậy, toàn vẹn của dữ liệu.

- Trong project này, tác giả lựa chọn mode STR, cấu hình tần số cho QSPI là 100MHz.

Hình 4: Tần số hoạt động của chip QSPI Flash MT25QL128

Hình 4: Tần số hoạt động của chip QSPI Flash MT25QL128

- Số bit cho dung lượng – dùng để cấu hình: Dung lượng nhớ của chip Flash MT25QL128 là 128 Mbits (hình 5) =16 MBytes = 224 bytes = 2n+1 bytes n = 23 . Số n sẽ là số chúng ta dùng cho việc cấu hình trong CubeMX.

Hình 5: Dung lượng nhớ của chip MT25QL128

Hình 5: Dung lượng nhớ của chip MT25QL128

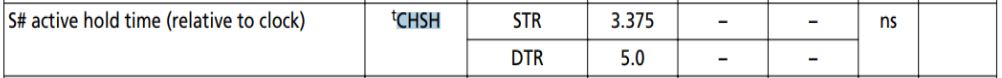

- Chip select high time (tCHSH): Đây thời gian mà tín hiệu chip select được giữ sau khi thực hiện xong 1 lệnh, ta cần phải cho đọc datasheet của bộ nhớ QSPI Flash mới có thể tính toán. Ví dụ, đối với bộ nhớ MT25QL128 là 3.375ns ở chế độ STR như hình 6; Giả sử bộ nhớ chạy ở tần số 100MHz thì chỉ cần chưa tới 1 chu kì thì ta có thể set bất kỳ số nào ≥1. Số lớn hơn giúp tăng độ tin cậy khi truyền dữ liệu nhưng sẽ làm giảm throughput của bus.

Hình 6: Chip select high time của chip QSPI Flash MT25QL128

Hình 6: Chip select high time của chip QSPI Flash MT25QL128

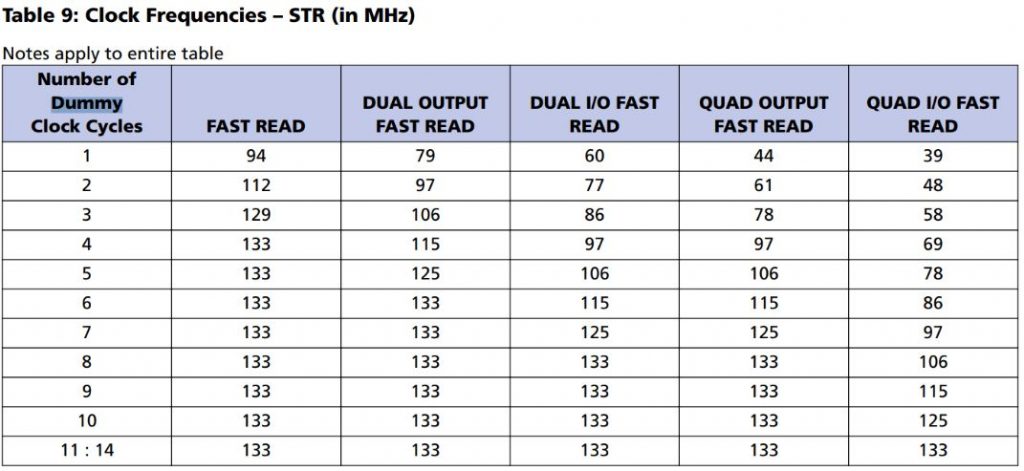

- Dummy cycle: Thời gian để chuyển đổi cái chân IO1➡4 từ input sang output. Hãy tưởng tượng, để đọc 4 bit từ 4 chân của QSPI Flash thì đầu tiên 4 chân IO này phải là input để nhận lệnh và địa chỉ; Sau đó, 4 chân IO này phải chuyển sang output để gửi dữ liệu đi; Vậy, việc chuyển từ in sang out cần 1 khoảng thời gian gọi là dummy cycles và tham số này chỉ có tác dụng đối với các lệnh đọc vì ghi thì ko cần chuyển đổi từ input sang output. Số chu kì máy cho khoảng dummy phụ thuộc vào loại lệnh đọc (FAST READ, DUAL I/O FAST READ, …), tần số hoạt động, chế độ STR hay DTR. Đối với chip MT25QL128 thì tham số này cho chế độ STR nằm trong Table 9: Clock Frequencies – STR như Hình 7.

Hình 7: Bảng Dummy Cycle cho chế độ STR

Hình 7: Bảng Dummy Cycle cho chế độ STR

– Ở trong project này, QSPI Flash chạy ở tần số 100MHz (gần 133MHz), chế độ “QUAD OUTPUT FAST READ”. Để đảm bảo dữ liệu ổn định nhất, tác giả sử dụng thông số là 10 dummy clock cycles.

– Qua phần này, ta đã nắm được 1 số thông số của 1 bộ nhớ QSPI và cách đọc chúng trong Datasheet.

Cấu hình ngoại vi cho QSPI Flash

– Ở phần này, ta sẽ đi cụ thể từng tham số và cách cấu hình trong giao diện CubeMX để STM32 giao tiếp được với QSPI Flash.

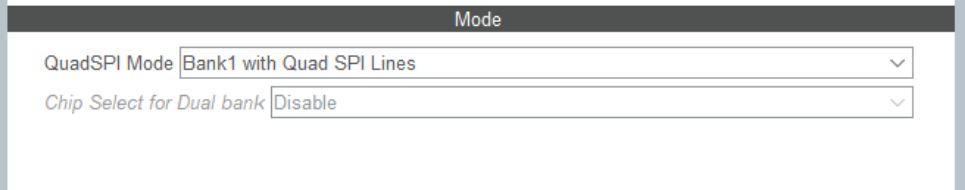

– Đầu tiên, ta kích hoạt ngoại vi QSPI với chế độ “Bank1 with Quad SPI Lines” như hình 8 dưới:

Hình 8: Kích hoạt ngoại vi QSPI

Hình 8: Kích hoạt ngoại vi QSPI

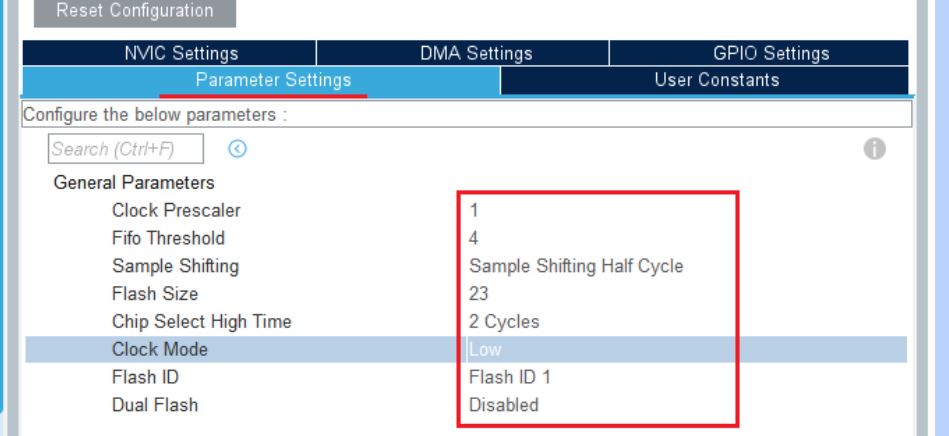

– Cấu hình các tham số ở tab “Parameter Settings”:

Hình 9: Cấu hình tab “Parameter Settings”

Hình 9: Cấu hình tab “Parameter Settings”

- Clock Prescaler: Ở đây ta nhập số 1 nghĩa là clock cho ngoại vi QSPI tương đương clock tổng (HCLK clock) chia 2. Ở bài viết này clock HCLK là 200MHz nên clock hoạt động cho QSPI Flash sẽ là 100MHz.

- Fifo Threshold: bộ đệm FIFO tính theo bytes. Trong bài viết này, tác giả để mặc định theo chương trình là 4 bytes. Điều này có nghĩa là nếu có >= 4 bytes cần ghi/đọc ở FIFO thì vi xử lý sẽ khởi tạo các lệnh đọc/ghi đối với Flash để giải phóng vùng nhớ trong FIFO. Theo tài liệu Reference Manual của chip STM32F746NGH6U, ở mục 14, trang 391 phần FIFO and data management thì độ rộng tối đa của FIFO là 32 bytes. Chúng ta có thể chọn lớn hơn 4 nhưng không nên quá lớn để tránh bộ đệm FIFO bị overrun (mất dữ liệu cũ) và vi điều khiển phải đọc lại tốn thời gian.

- Sample Shifting (chỉ áp dụng với mode STR): vi xử lý sẽ đọc dữ liệu ở sườn xuống của xung clock thay vì sườn lên. Điều này đảm bảo độ ổn định khi đọc dữ liệu trong trường hợp bộ nhớ Flash nằm xa vi điều khiển hoặc thiết kế board mạch không đảm bảo chất lượng.

- Flash Size: Ở mục 2 phần số bit dung lượng, chúng ta đã thấy qua cách tính ra số mũ cho 2n+1 bytes dung lượng bộ nhớ. Ta tính ra được n = 23 và đây là con số ta sẽ điền vào ô này.

- Chip Select High Time: Đây là thời gian chờ khi vi điều khiển muốn thực hiện 2 lệnh liên tiếp nhau. Ở phần trên, tại mục Chip select high time (tCHSH) ta cũng đã có đề cập đến. Ta tính ra được cần ít nhất 1 chu kì, tuy nhiên để chắc chắn, tác giả đã để là 2 chu kì. Người dùng có thể set cao hơn nếu muốn (thanh ghi cấu hình của STM32NGH6U cho phép cấu hình cao nhất là 8 chu kì), tuy nhiên, nếu số quá cao so với cần thiết thì vi điều khiển sẽ lãng phí thời gian chờ giữa 2 lệnh.

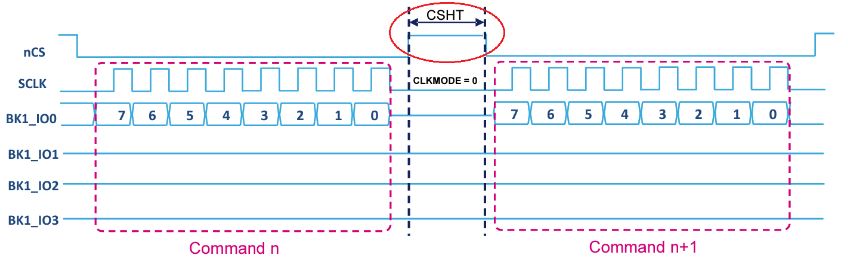

- Clock Mode: Phần này quyết định trạng thái clock khi vi xử lý đang chờ giữa 2 lệnh. Nếu ta để là “High”, thì khi ở giai đoạn chờ trước khi gửi lệnh mới tới Flash, xung clock sẽ được giữ ở mức cao (không dao động nữa) như ở hình 10 và ngược lại. Điều này có ích nếu chúng ta có nhiều hơn 2 thiết bị dùng chung giao diện QSPI vì nó đảm bảo chắc chắn tín hiệu chip select chỉ active khi thực sự có lệnh cần gửi đi.

Hình 10: Clock Mode “High”

Hình 10: Clock Mode “High”

- Flash ID: Chúng ta để mặc định. Chỉ khi dùng Dual Flash thì ta mới cần quan tâm đến tham số này.

- Dual Flash: Disabled. Chỉ khi dùng Dual Flash thì ta mới cần quan tâm đến tham số này.

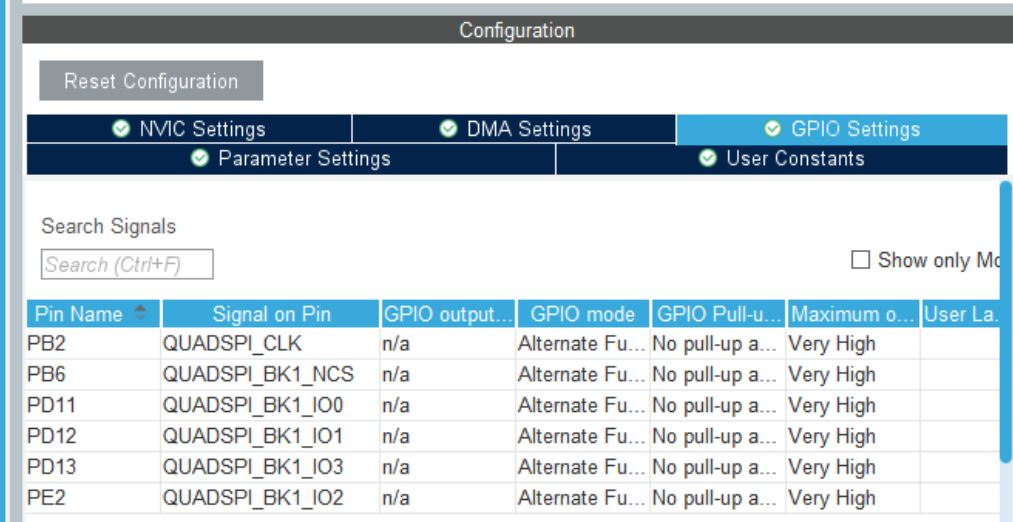

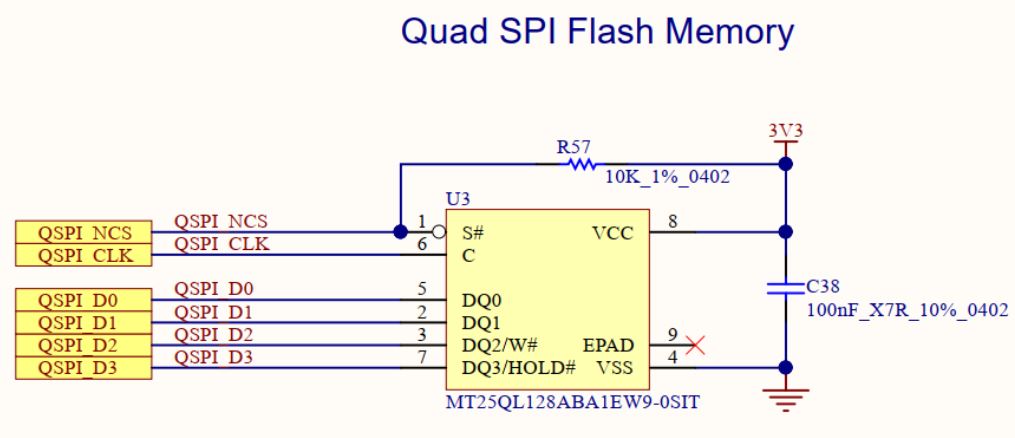

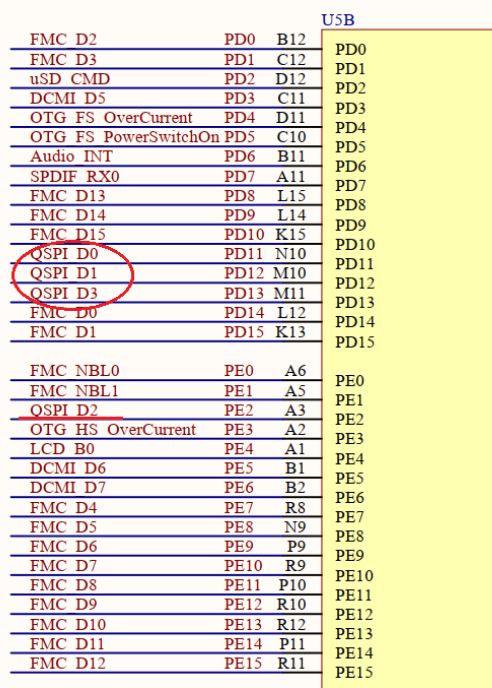

- Cấu hình chân: Đối với board STM32F746NGH6U DISCO thì ta cần cấu hình chân như hình 11 dưới. Để biết được chân nào thì ta cần dựa vào sơ đồ nguyên lý của board như ở hình 12 và 13.

Hình 11: Cấu hình chân QSPI Flash cho STM32F746NGH6U DISCO

Hình 11: Cấu hình chân QSPI Flash cho STM32F746NGH6U DISCO

Hình 12: Sơ đồ nguyên lý nối chân tại bộ nhớ QSPI Flash

Hình 12: Sơ đồ nguyên lý nối chân tại bộ nhớ QSPI Flash

Hình 13: Sơ đồ nguyên lý nối chân tại vi điều khiển

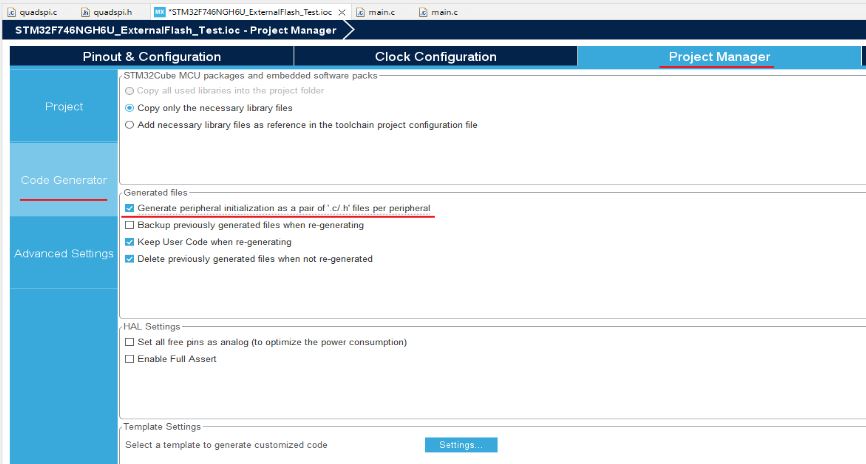

Ngoài ra, ta nên tách các hàm khởi động thành các cặp file “.c/.h” bằng cách chọn option như ở hình 14:

Hình 14: Tách thư viện cấu hình cho ngoại vi thành cặp file “.c/.h”

Hình 14: Tách thư viện cấu hình cho ngoại vi thành cặp file “.c/.h”

Để hiểu rõ thêm về phần cấu hình ngoại vi, các bạn tham khảo thêm bài hướng dẫn của ST [2] và bài hướng dẫn cấu hình trực tiếp thanh ghi cho ngoại vi QSPI [3]

Các nội dung liên quan đến chế độ hoạt động của QSPI Flash, các hàm hỗ trợ của thư viện STM32 HAL sẽ được trình bày tại phần tiếp theo.

Tài liệu tham khảo:

[1] https://datasheetspdf.com/pdf-file/1225530/Micron/MT25QL128ABA/1

[2] https://www.st.com/resource/en/application_note/an4760-quadspi-interface-on-stm32-microcontrollers-and-microprocessors–stmicroelectronics.pdf

[3] https://vivonomicon.com/2020/08/08/bare-metal-stm32-programming-part-12-using-quad-spi-flash-memory/

Tổng hợp hướng dẫn Internet of Things với NodeMCU ESP8266 và ESP32

Nhóm tác giả

Ng.Q.Phương

Ng.H.N.Thương

Ng.H.Phúc