Memory Protection Unit (MPU) là một mô-đun ngoại vi của nhiều dòng vi xử lý ARM Cortex-M. MPU có nhiệm vụ thiết lập đặc tính cho các vùng nhớ khác nhau. Ở lõi ARM-Cortex M7 thì MPU hỗ trợ cài đặt thuộc tính cho tối đa 8 hoặc 16 phân vùng khác nhau tùy thuộc vào dòng chip. Đối với vi điều khiển STM32F746NGH6U thì tối đa là 8 vùng nhớ và có thể cài đặt thông qua công cụ cấu hình CubeMX. Khi các quy tắc của MPU bị vi phạm, MemManage Exception sẽ được kích hoạt, các lỗi vi phạm quy tắc MPU có thể không ảnh hưởng đến luồng hoạt động của chương trình, nghĩa là chương trình vẫn có thể chạy bình thường nếu ta tắt MPU đi.

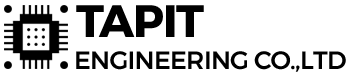

Hình 1: Các mô-đun phần cứng trong xử lý Cortex-M7

Hình 1: Các mô-đun phần cứng trong xử lý Cortex-M7

Các đặc tính của 1 vùng nhớ được MPU quản lý

1. Địa chỉ bắt đầu và dung lượng bộ nhớ

- Địa chỉ bắt đầu là nơi bắt đầu mà vùng nhớ cần phải cài đặt thuộc tính. Ví dụ biến X bắt đầu từ địa chỉ 0x90002000 thì người dùng có thể cài đặt địa chỉ bắt đầu là 0x90002000

- Dung lượng: Khoảng không gian vùng nhớ mà người dùng cần cài đặt thuộc tính. Dung lượng nhỏ nhất là 1 KB và lớn nhất là 4 GB và được tính theo bậc 2 mũ ví dụ: 1 KB, 2 KB, 4 KB, 8 KB, 16 KB, 32 KB, 64 KB,…

- Với 2 tham số này, ta có thể xác định được vùng nhớ cần phải cài đặt các thuộc tính.

2. Cacheable, Bufferable, Shareable, XN (instruction execution permission)

- Shareable: Đối với vùng nhớ được cài đặt là Shareable thì hệ thống memory sẽ hỗ trợ việc truyền dữ liệu giữa các master khác nhau và có thể sẽ đảm bảo việc đồng nhất dữ liệu trong trường hợp có Cache. Vì STM32F7 không có các protocol được implement dưới phần cứng để đảm bảo được Cache Coherency nên khi một vùng nhớ được cài đặt là Shareable thì Data Cache sẽ bị disable cho vùng nhớ đó.

- XN (Execute Never): Với tính chất này, vi xử lý sẽ không được phép đọc và thực thi lệnh trong vùng nhớ được cài đặt XN. Nếu vi xử lý cố gắng thực thi thì Hardfault (Memmanage fault) sẽ được kích hoạt.

- Cacheable: Cho phép lõi vi xử lý lưu các dữ liệu thường xuyên dùng trong Data Cache và Instruction Cache.

- Bufferable: Cho phép các dữ liệu trong vùng nhớ được ghi vào Writebuffer của cache giảm tần suất Cache phải truy cập vào bộ nhớ chính (RAM).

- TEX: Đây là một tham số được định nghĩa bởi lõi vi xử lý, tham số này cùng với các bit Cacheable, Shareable,… sẽ thiết lập nên đặc tính tương ứng cho từng vùng nhớ cụ thể.

Để hiểu chính xác hơn về các thuộc tính (attribute) và cách dùng chính mời các bạn coi qua video theo link ở phần tham khảo [https://www.youtube.com/watch?v=6IUfxSAFhlw]

3. Đảm bảo tính nhất quán dữ liệu và ảnh hưởng của MPU lên hiệu năng

- Để hiểu nội dung này, cùng tìm hiểu về “speculative read”, speculative read có thể xem như vi xử lý “Cầm đèn chạy trước ôtô”! Vi xử lý sẽ cố gắng đọc các dữ liệu và lệnh tiếp theo dữ liệu/lệnh đang trong quá trình thực thi. Có thể sau đó vi xử lý không cần dùng đến chúng nhưng nó vẫn sẽ đọc. Điều này cho phép vi điều khiển đáp ứng ngay lập tức nêu các dữ liệu được xử lý sớm đó được dùng. Tuy nhiên, điều này gây ra 1 số vấn đề khi thực thi chương trình như truy cập vào vùng nhớ không được phép, thực thi lệnh từ vùng nhớ dữ liệu,… do lúc này thứ tự đọc trong bộ nhớ đã disorder (không theo thứ tự)

- Bên cạnh đó, mọi người cũng cần hiểu về 3 khái niệm về loại bộ nhớ:

- Loại Normal: Vi xử lý có thể đọc, đọc trước và thay đổi thứ tự việc đọc/ghi dữ liệu trong bộ nhớ để tăng hiệu năng thực thi chương trình

- Loại Device và loại Strongly-ordered: Thứ tự đọc/ghi/thực thi phải được tuân thủ đúng theo thứ tự trong chương trình để đảm bảo dữ liệu không bị xáo trộn, hỏng và đồng nhất dữ liệu

- Một số kết luận được rút ra như sau:

- Loại normal sẽ hiệu quả khi vi xử lý cần thực thi các instruction nhờ việc cho phép thực hiện các speculative read và lưu các dữ liệu vào cache trước khi chúng cần.

- Loại device và strongly-ordered không cho phép “speculative read”, nêu instruction được thi thi từ trong vùng này thì instruction n phải được thực thi xong thì instruction n+1 mới được thực thi.

- Loại device thông thường là các nhóm thanh ghi cấu hình/điều khiển của các ngoại vi hay mô-đun phần cứng trong vi xử lý.

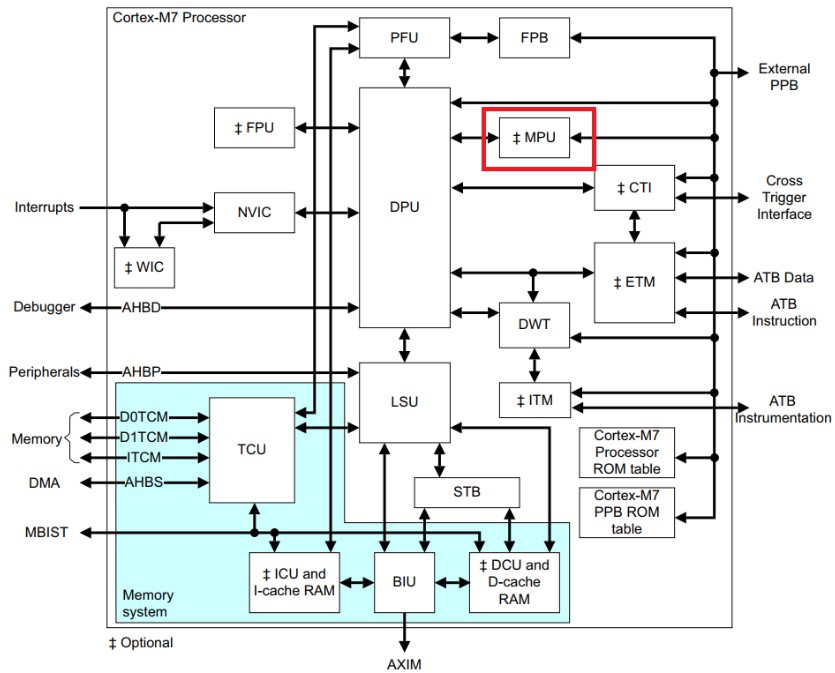

Tham khảo một bảng thuộc tính của một số loại vùng nhớ như sau:

Hình 2: Phân loại hành vi đối với các chip nhớ, ngoại vi

Hình 2: Phân loại hành vi đối với các chip nhớ, ngoại vi

- RAM ngoài thường được sắp xếp là Normal nghĩa là chúng có thể được sử dụng như RAM bình thường!

- QSPI Flash thường được xếp là loại “External device”, nghĩa là việc thực thi lệnh từ bộ nhớ ngoài không được khuyến khích hoặc sẽ làm giảm hiệu năng thiết bị do chúng phải hạn chế các “speculative read”

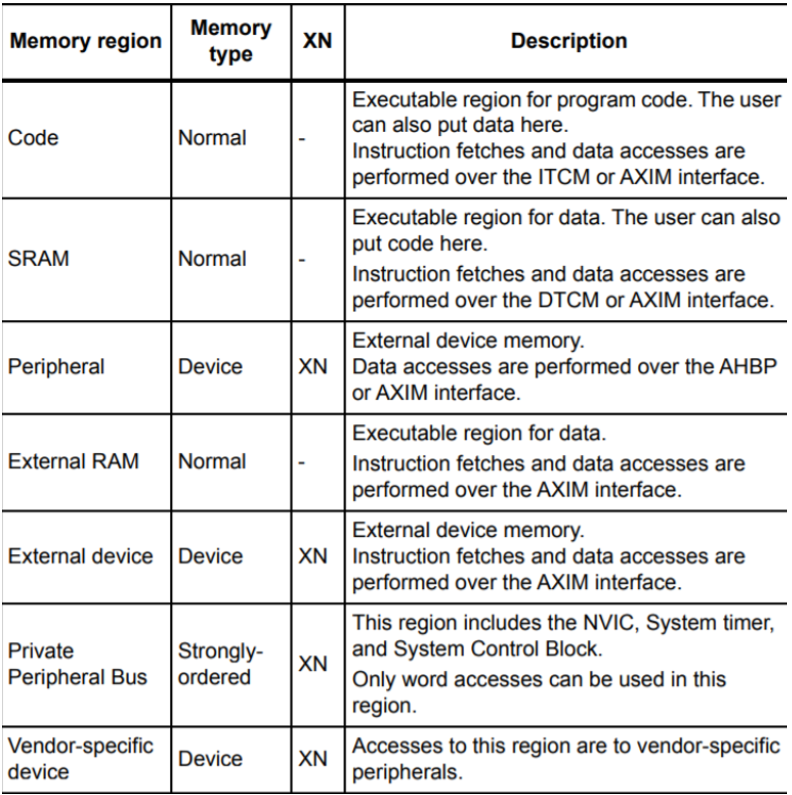

Tham khảo bảng cấu hình MPU cho một số loại vùng nhớ cùng với đặc tính của chúng:

Hình 3: Cấu hình MPU cho một số loại vùng nhớ

Hình 3: Cấu hình MPU cho một số loại vùng nhớ

Dựa vào bảng trên, ta giả sử cần phải khai báo một DMA buffer nằm trong SDRAM thì vì SDRAM thuộc loại Normal và để đảm bảo Cache Coherency, cần disable cache, vậy setting của vùng nhớ sẽ là: Normal, Non-cacheable và Shareable (vì cả Cortex-M7 và DMA đều phải sử dụng vùng nhớ này). MPU cần được cài đặt như dòng 5 trong hình (TEX = 001, C = 0, B = 0, S = 1).

Tham khảo thêm một số cài đặt được recommend bởi ST. Để thuận tiện và dễ hiệu, các bạn coi video sau [https://www.youtube.com/watch?v=6IUfxSAFhlw] ở các đoạn dưới:

- Cấu hình MPU cho QSPI Flash: Từ phút thứ 15 đến phút thứ 16

- Cấu hình MPU cho FMC SDRAM: Từ 16’08” đến 16’50”

- Cấu hình MPU cho vùng nhớ buffer trên RAM có sử dụng DMA: Từ 16’52 đến phút thứ 18

Nhóm tác giả

Ng.Q.Phương, Ng.H.Phúc, Ng.H.N.Thương