Vi điều khiển STM32F411 tính hợp hai bộ ngoại vi Watchdog là Independent Watchdog (IWDG) và Window Watchdog(WWDG) với độ chính xác cao và khả năng áp dụng linh hoạt trong các ứng dụng. Cả hai bộ Watchdog này đều được sử dụng phát hiện và giải quyết các sự cố do lỗi phần mềm, từ đó kích hoạt khởi động lại vi điều khiển hoặc thực thi một chương trình ngắt (chỉ có ở Window Watchdog) khi tổng thời gian mà bộ đếm (counter) của watchdog chạm đến giá trị timeout đã được cấu hình trước.

[HỌC ONLINE: LẬP TRÌNH VI ĐIỀU KHIỂN STM32, VI XỬ LÝ ARM CORTEX – M]

Bài viết này cung cấp những nội dung để các có thể hiểu được về cấu trúc, cách hoạt động của IWDG và hướng dẫn sử dụng IWDG với một bài tập thực hành đơn giản, dễ hiểu.

I. Mô tả hoạt động:

I. Mô tả hoạt động:

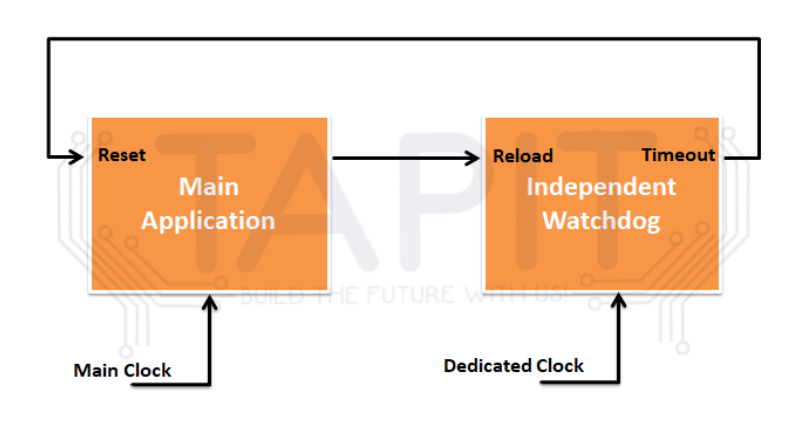

Khối Independent Watchdog bao gồm một Counter thực hiện đếm xuống từ một giá trị reload ban đầu được người dùng nạp sẵn. Nếu Counter này đếm về 0 (timeout) thì khối Independent Watchdog sẽ tạo tín hiệu làm reset vi điều khiển. Vì vậy trong quá trình hoạt động, vi điều khiển phải định kỳ thực hiện việc reload để nạp lại giá trị cho counter trước khi xảy ra timeout.

Trong quá trình hoạt động của vi điều khiển, nhiễu hoặc lỗi phần mềm có thể là nguyên nhân dẫn đến vi điều khiển bị treo, điều này làm cho counter của bộ IWDG không thực hiện được reload kịp thời và timeout, lúc này vi điều khiển sẽ reset và hoạt động lại từ đầu.

II. Cấu trúc của IWDG

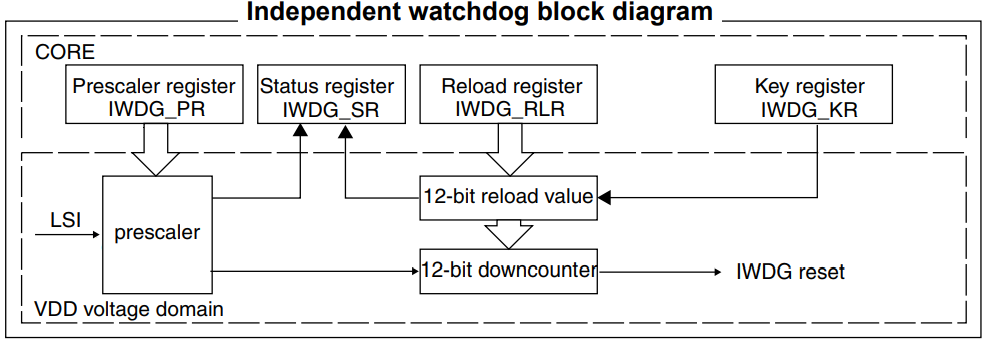

– Nguồn cung cấp cho IWDG là từ VDD domain nên khối này vẫn hoạt động kể cả khi đưa vi điều khiển vào chế độ tiết kiệm năng lượng STOP hay STANDBY.

– Nguồn cung cấp cho IWDG là từ VDD domain nên khối này vẫn hoạt động kể cả khi đưa vi điều khiển vào chế độ tiết kiệm năng lượng STOP hay STANDBY.

– Tính năng bảo vệ: Việc ghi giá trị vào thanh ghi Prescaler IWDG_PR và thanh ghi Reload IWDG_RLR được bảo vệ bởi thanh ghi Key IWDG_KR. Để có thể thay đổi giá trị các thanh ghi được bảo vệ thì cần ghi giá trị 0x5555 vào thanh ghi IWDG_KR trước, sau đó mới khi ghi giá trị mong muốn vào thanh ghi IWDG_PR hoặc thanh ghi IWDG_RLR. Bên cạnh đó, thanh ghi IWDG_KR còn có các nhiệm vụ sau:

+ Bắt đầu IWDG nếu nhận giá trị 0xCCCC

+ Reload lại giá trị counter bằng với giá trị của thanh ghi IWDG_RLR nếu nhận giá trị 0xAAAA.

– IWDG sử dụng bộ dao động từ bộ dao động nội tần số thấp (LSI) nên IWDG vẫn hoạt động ngay cả khi nguồn dao động chính của vi điều khiển bị hỏng, nguồn clock này được đưa qua 1 bộ chia tần – prescaler trước khi làm cho counter đếm xuống.

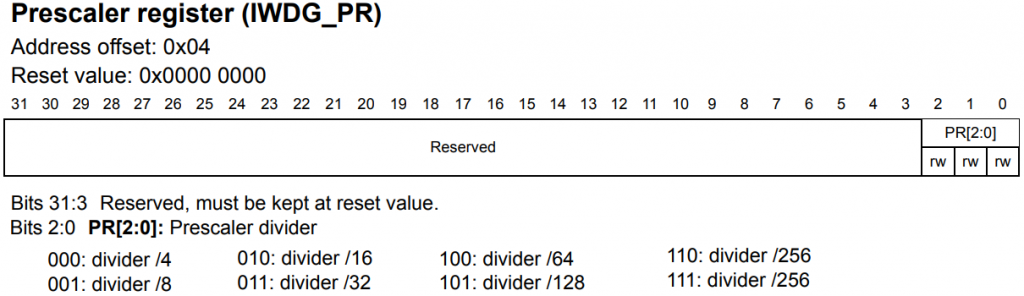

– Giá trị của bộ chia tần được cấu hình bởi 3 bit trọng số thấp của thanh ghi Prescaler để cấu hình giá trị chia tần số HSI đầu vào, để tạo tần số đếm xuống cho downcounter.

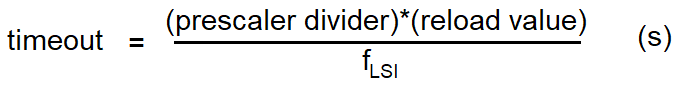

– Thời gian timeout phụ thuộc vào tần số sau bộ prescaler, giá trị reload, được tính theo công thức sau:

– Thời gian timeout tối thiểu và tối đa của IWDG ở đơn vị ms khi tần số LSI là 32kHz, downcounter 12bit:

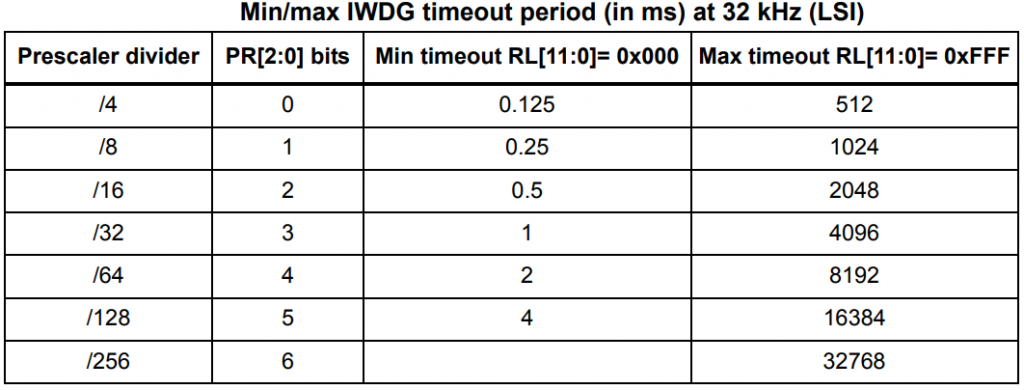

– Giá trị reload được cấu hình bởi 12bit trọng số thấp của thanh ghi IWDG_RLR, giá trị nạp này được vào downcounter mỗi khi thanh ghi IWDG_RLR nhận giá trị 0xAAAA. Từ thời gian timeout mong muốn, người dùng sẽ tính toán ra giá trị của thanh ghi Reload. Nếu không cấu hình thì mặc định khi reset của thanh ghi này là 0xFFF.

III.Thực hành ứng dụng:

Cấu hình bài thực hành về ứng dụng IWDG như sau: 1 led PD12 báo hiệu MCU đang hoạt động bình thường hay bị reset, 1 nút nhấn PA0 để đưa MCU vào chế độ treo để thực hiện reset MCU bằng IWDG và thời gian timeout của IWDG là 2s.

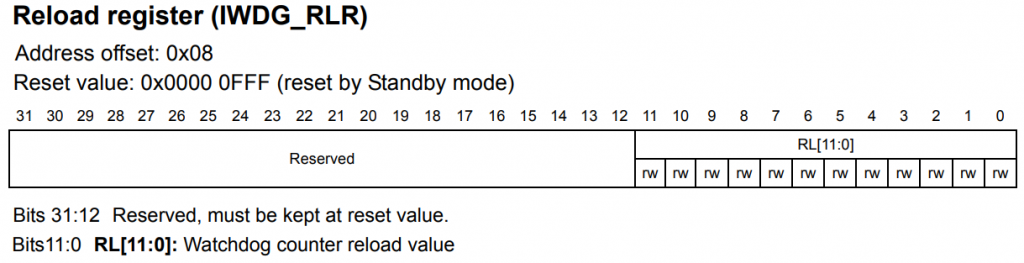

Bước 1: Kích chọn dòng STM32F411VETx và sau đó chọn “Start Project”.

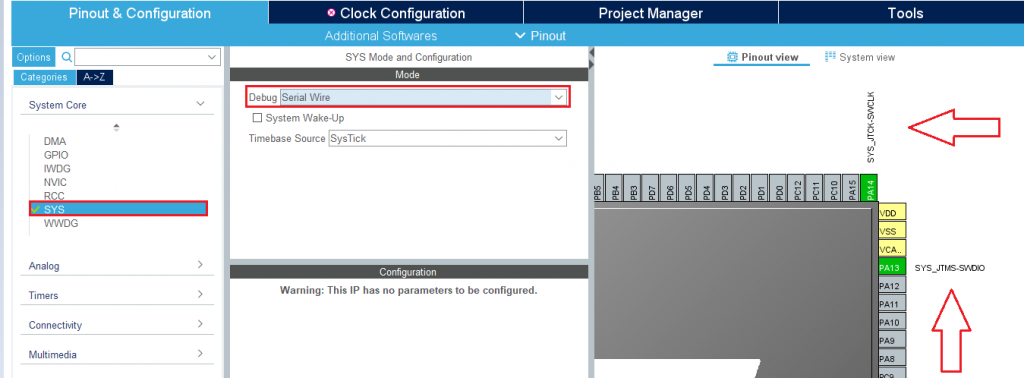

Bước 2: Chọn Serial Wire để nạp code

Bước 3: Click chuột phải vào chân PD12 sau đó tích vào ô GPIO_Output

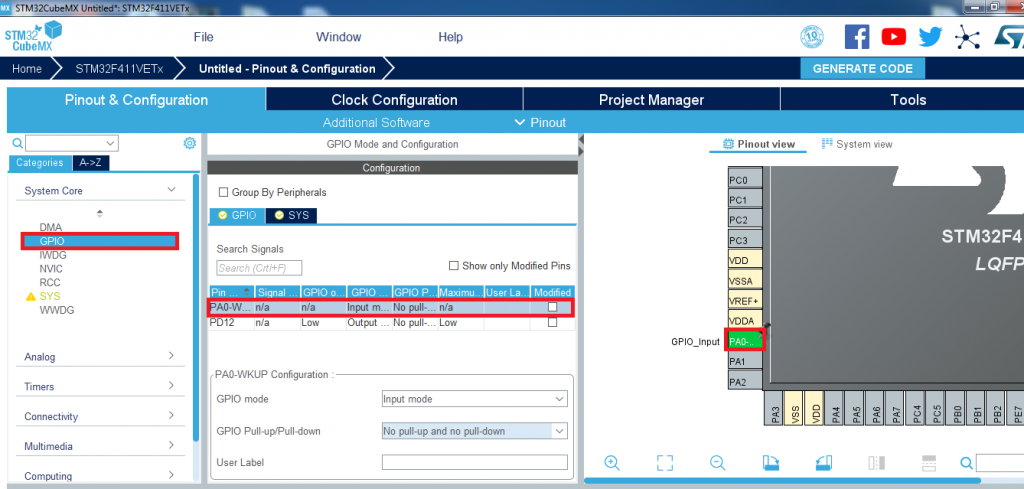

Bước 4: Click chuột phải vào chân PA0 sau đó tích vào ô GPIO_Input

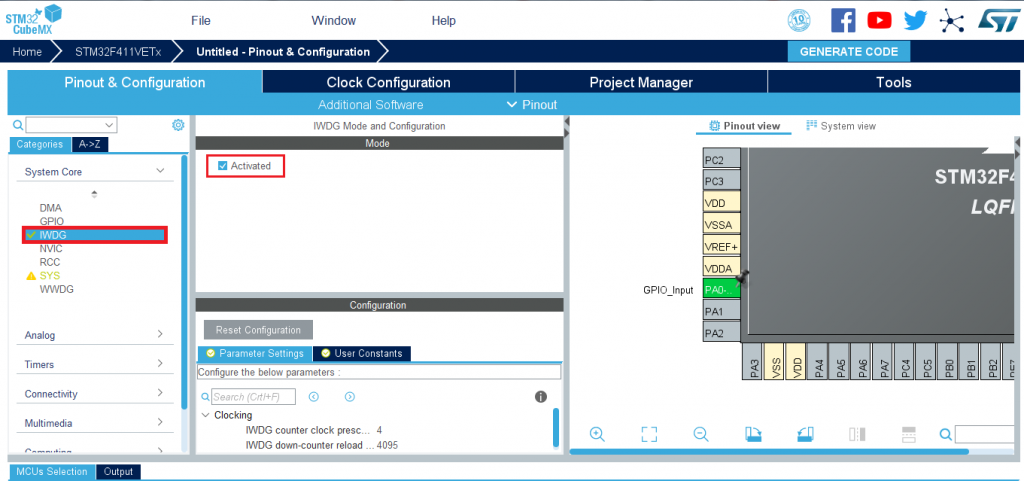

Bước 5: Click chọn ô Activated để sử dụng IWDG cho project này

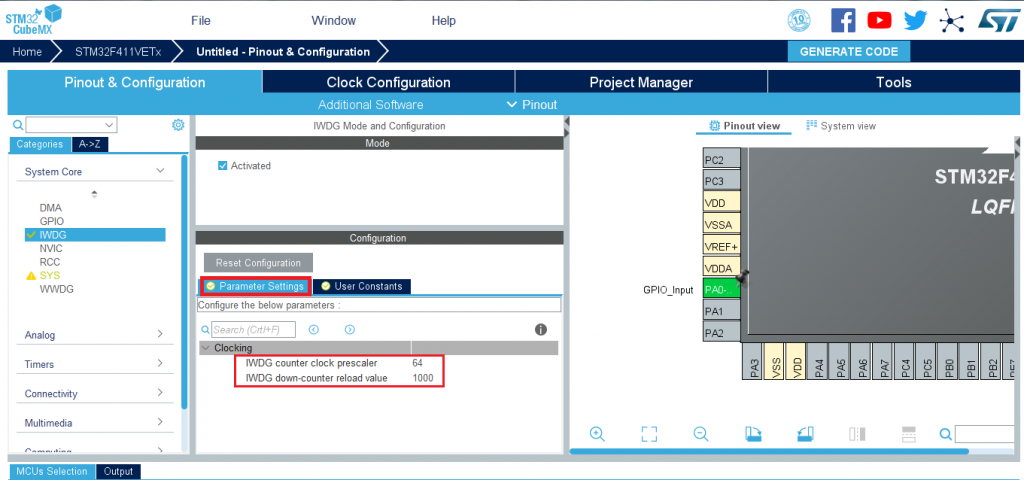

Bước 6: Cấu hình timeout cho tính năng IWDG

Với Prescaler = 64, Reload value = 1000, f của bộ LSI = 32 KHz áp dụng công thức tính thời gian timeout ở trên ta có t = 2s

Bước 7: Cấu hình Project ở mục Project Manager và sinh code

Bước 8: Code

Ở hàm while(1):

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

/* USER CODE BEGIN WHILE */ while (1) { /* USER CODE END WHILE */ /* USER CODE BEGIN 3 */ HAL_GPIO_TogglePin(GPIOD, GPIO_PIN_12); //MCU dao led 0,5s de bao hoat dong binh thuong HAL_Delay(500); IWDG->KR = 0xAAAA; //Reload counter if(HAL_GPIO_ReadPin(GPIOA, GPIO_PIN_0) == GPIO_PIN_SET) //Neu nhan nut { HAL_GPIO_WritePin(GPIOD, GPIO_PIN_12, GPIO_PIN_SET); //Sang led trong vong 2s while(1); //Treo MCU } } /* USER CODE END 3 */ |

Bước 9: Build và Load chương trình.

TAPIT ARM R&D