Công suất và năng lượng tiêu thụ của MCU ảnh hưởng đến các quyết định thiết kế về nguồn, thời gian sử dụng pin, và kể cả nhiệt độ hoạt động trong các ứng dụng nhúng. Nhất là khi đối mặt với các ứng dụng được cung cấp năng lượng từ nguồn pin, người thiết kế phải tối ưu để đảm bảo thời gian sử dụng là lâu nhất có thể.

Hầu hết MCU hiện nay được thiết kế dựa vào công nghệ CMOS – Bên trong MCU có hàng triệu CMOS. Nếu các bạn hiểu về cấu trúc, sự tiêu thụ năng lượng của CMOS thì các bạn có thể thực hiện tốt hơn việc tối ưu năng lượng bằng cách chọn được MCU phù hợp, đồng thời có những cấu hình phần cứng và cách lập trình firmware tốt nhất.

Từ kiến thức tích lũy được của cá nhân qua các tài liệu của hãng ST, TI và từ các môn học như VLSI, mình tóm lượt 1 số ý chính trong post này và chia sẻ đến các bạn giúp các bạn có thể áp dụng và tìm hiểu sâu hơn về chủ đề này.

—————-

Tổng tiêu hao công suất trên 1 CMOS được phân tích thành hai thành phần là công suất động và công suất tĩnh. Công suất động xuất hiện khi cổng chuyển trạng thái, công suất tĩnh xảy ra ngay cả khi thiết bị ở trạng thái nghỉ.

I/CÔNG SUẤT ĐỘNG gồm công suất chuyển mạch và công suất ngắn mạch, trong đó:

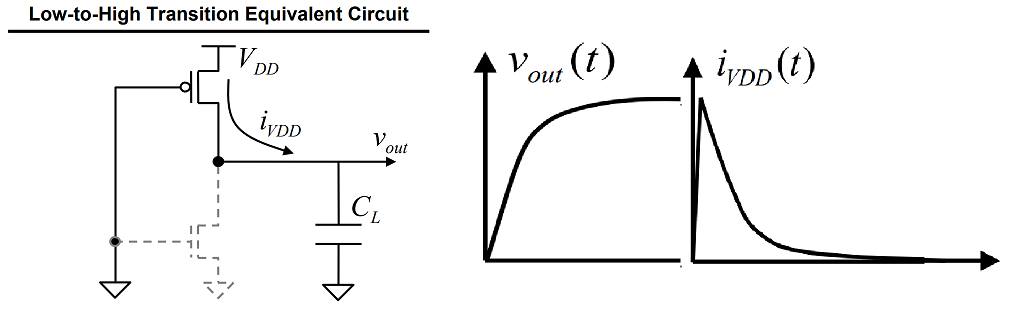

*Công suất chuyển mạch: là công suất cần có để nạp cho điện dung ký sinh đến điện áp VDD. Công suất này tỷ lệ với tần suất chuyển mạch.

Hầu hết MCU hiện nay được thiết kế dựa vào công nghệ CMOS – Bên trong MCU có hàng triệu CMOS. Nếu các bạn hiểu về cấu trúc, sự tiêu thụ năng lượng của CMOS thì các bạn có thể thực hiện tốt hơn việc tối ưu năng lượng bằng cách chọn được MCU phù hợp, đồng thời có những cấu hình phần cứng và cách lập trình firmware tốt nhất.

Từ kiến thức tích lũy được của cá nhân qua các tài liệu của hãng ST, TI và từ các môn học như VLSI, mình tóm lượt 1 số ý chính trong post này và chia sẻ đến các bạn giúp các bạn có thể áp dụng và tìm hiểu sâu hơn về chủ đề này.

—————-

Tổng tiêu hao công suất trên 1 CMOS được phân tích thành hai thành phần là công suất động và công suất tĩnh. Công suất động xuất hiện khi cổng chuyển trạng thái, công suất tĩnh xảy ra ngay cả khi thiết bị ở trạng thái nghỉ.

I/CÔNG SUẤT ĐỘNG gồm công suất chuyển mạch và công suất ngắn mạch, trong đó:

*Công suất chuyển mạch: là công suất cần có để nạp cho điện dung ký sinh đến điện áp VDD. Công suất này tỷ lệ với tần suất chuyển mạch.

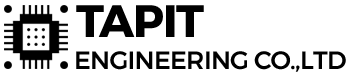

*Công suất ngắn mạch: Do độ dốc của sườn lên và sườn xuống của xung đầu vào khi quá trình chuyển mạch xảy ra từ logic 0 -> 1 hoặc 1-> 0 thì GND và VDD thông nhau trong một khoảng thời gian rất ngắn trong quá trình chuyển trạng thái đó.

==> Công suất ngắn mạch này có thể được giảm khi giảm độ dốc của xung đầu vào (phụ thuộc vào thiết kế) hoặc giảm điện áp nguồn cung cấp hay giảm số lần chuyển mạch.

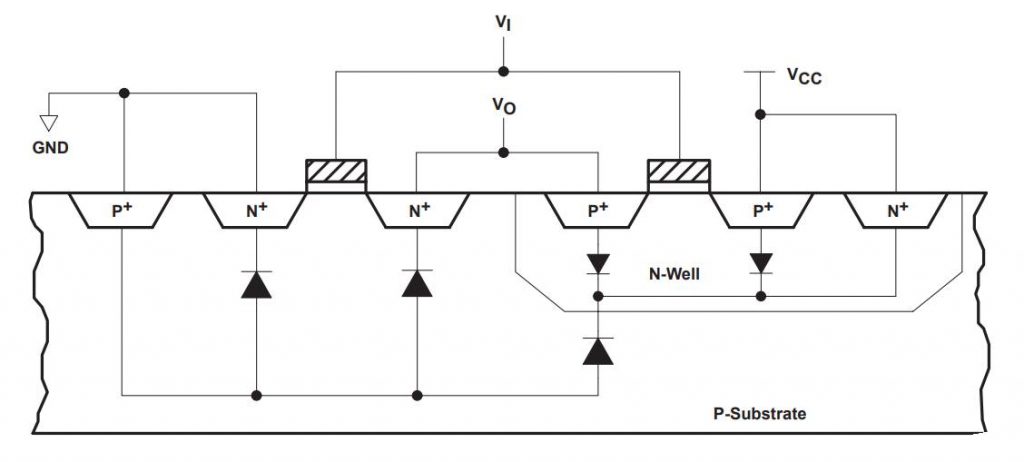

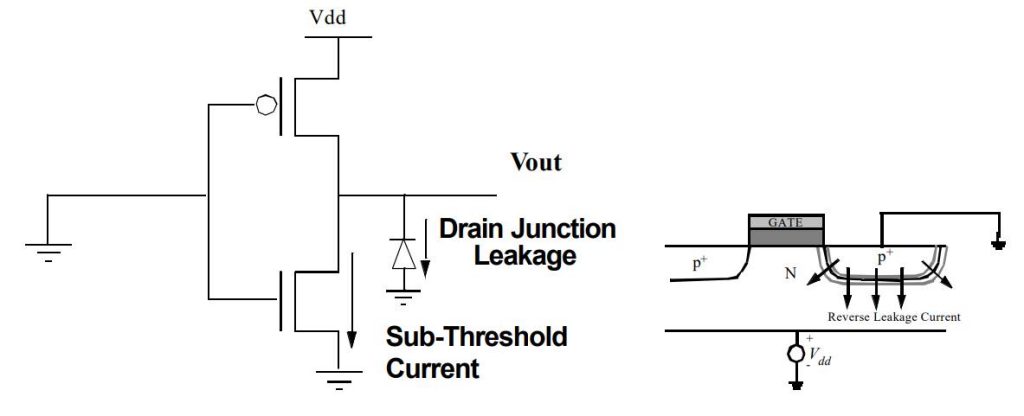

II/CÔNG SUẤT TĨNH gồm công suất tĩnh do dòng rò.

*Công suất tĩnh do dòng rò: Xảy ra ngay cả khi không có chuyển mạch, do dòng rò của các tiếp giáp PN (diode ký sinh) phân cực ngược giữa vùng khuếch tán và vùng nền ở bên dưới cực nguồn và cực máng. Dòng ngược qua tiếp giáp PN sẽ tăng khi nhiệt độ tăng.

*Công suất tĩnh do dòng rò: Xảy ra ngay cả khi không có chuyển mạch, do dòng rò của các tiếp giáp PN (diode ký sinh) phân cực ngược giữa vùng khuếch tán và vùng nền ở bên dưới cực nguồn và cực máng. Dòng ngược qua tiếp giáp PN sẽ tăng khi nhiệt độ tăng.

==> Ngoài công suất tĩnh do dòng rò thì còn có thành phần dòng dưới ngưỡng (subthreshold) có ảnh hưởng lớn. Dòng rò này phụ thuộc vào công nghệ và thiết kế CMOS.

——————————-

Từ các cơ sở trên chúng ta có thể thấy được công suất tiêu thụ của một MCU phụ thuộc vào các yếu tố sau:

* Kích cỡ của MCU: Công nghệ sử dụng, số lượng transistor, các ngoại vi được tích hợp bên trong vi điều khiển càng nhiều thì càng xuất hiện nhiều CMOS.

* Điện áp cung cấp cho MCU (VDD): Công suất sử dụng của các CMOS tỉ lệ thuật với bình phương điện áp VDD, cho nên có thể giảm được điện năng tiêu thụ bằng cách hạ thấp điện áp VDD.

* Tần số clock: Công suất tiêu thụ có thể được giảm đi bằng cách giảm tần số hoạt động của vi điều khiển (sử dụng tần số phù hợp với yêu cầu của ứng dụng).

*Chế độ hoạt động: Vi điều khiển cung cấp nhiều chế độ hoạt động tương ứng với nhiều mức tiêu hao năng lượng khác nhau bằng cách điều khiển khối nguồn hoặc bộ giao động đến CPU hay các ngoại vi.

——————————-

Từ các cơ sở trên chúng ta có thể thấy được công suất tiêu thụ của một MCU phụ thuộc vào các yếu tố sau:

* Kích cỡ của MCU: Công nghệ sử dụng, số lượng transistor, các ngoại vi được tích hợp bên trong vi điều khiển càng nhiều thì càng xuất hiện nhiều CMOS.

* Điện áp cung cấp cho MCU (VDD): Công suất sử dụng của các CMOS tỉ lệ thuật với bình phương điện áp VDD, cho nên có thể giảm được điện năng tiêu thụ bằng cách hạ thấp điện áp VDD.

* Tần số clock: Công suất tiêu thụ có thể được giảm đi bằng cách giảm tần số hoạt động của vi điều khiển (sử dụng tần số phù hợp với yêu cầu của ứng dụng).

*Chế độ hoạt động: Vi điều khiển cung cấp nhiều chế độ hoạt động tương ứng với nhiều mức tiêu hao năng lượng khác nhau bằng cách điều khiển khối nguồn hoặc bộ giao động đến CPU hay các ngoại vi.

Vậy là mình đã giới thiệu các bạn những nguyên nhân gây tiêu hao công suất động và công suất tĩnh trên CMOS. Nắm rõ các kiến thức này giúp chúng ta biết lựa chọn MCU, cấu hình thiết bị và cách lập trình firmware phù hợp để có thể tối ưu công suất và năng lượng tiêu thụ trong quá trình thiết bị hoạt động. Các bạn và mình có thể cùng nhau thảo luận về chủ đề này nhé!

Chúc các bạn thành công!

Thuong Nguyen