Bên cạnh khả năng phát hiện nhiễu hay lỗi phần mềm làm chương trình nhúng bị treo hoặc thực hiện lệnh trễ hơn bình thường như tính năng của khối Independent Watchdog (IWDG), thì Window Watchdog Timer (WWDG) còn có khả năng phát hiện được lỗi làm cho lệnh bị thực thi sớm hơn dự kiến. Khối watchdog này sẽ tạo tín hiệu reset MCU khi gặp các trường hợp trên. Không chỉ vậy, một yêu cầu ngắt để MCU thực hiện một số lệnh an toàn hay lưu trữ các thông tin cần thiết trước khi reset cũng được hỗ trợ nếu được người dùng cấu hình cho phép Early wakeup interrupt (EWI).

[HỌC ONLINE: LẬP TRÌNH VI ĐIỀU KHIỂN STM32, VI XỬ LÝ ARM CORTEX – M]

I. Cấu trúc và hoạt động của khối Window Watchdog

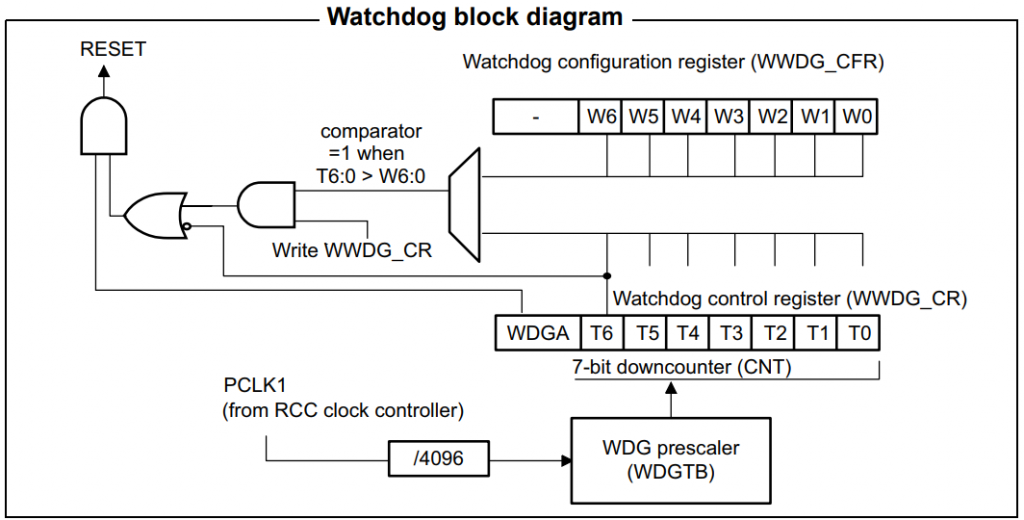

– Từ sơ đồ khối trên, ta có thể thấy được tín hiệu reset vi điều khiển sẽ được tạo ra khi có các trường hợp sau:

+ Bit T6 của thanh ghi watchdog control register (WWDG_CR) có giá trị 0. Bit T6:0 của thanh ghi WWDG_CR hoạt động như một downcounter 7 bit. Với giá trị đếm lớn nhất là 0x7F và nhỏ nhất là 0x3F vì lúc này bit T6 =0 và vi điều khiển bị reset. Vậy giá trị 0x3F chính là ngưỡng dưới của window watchdog. Chương trình chính phải thực hiện reload lại downcounter trước khi counter này chạm giá trị 0x3F.

+ Thực hiện lệnh ghi vào thanh ghi WWDG_CR (nạp lại giá trị của downcounter) trong khi giá trị các bit T6:0 của thanh ghi WWDG_CR lớn hơn giá trị các bit W6:0 của thanh ghi WWDG_CFR. Bit W6:0 của thanh ghi WWDG_CFR được sử dụng làm ngưỡng trên của window watchdog, vì nếu chương trình thực hiện việc nạp giá trị của downcounter khi giá trị của nó lớn hơn W6:0 thì vi điều khiển bị reset.

Sơ đồ sau đây sẽ giúp bạn hiểu rõ hơn về khoảng thời gian downcounter được reload (Refresh allowed) mà không làm cho MCU bị reset:

Trong đó:

+ t_WWDG là thời gian timeout

+ t_PCLK1 là chu kỳ clock APB1 ở đơn vị ms

+ 4096 là giá trị bộ chia tần cố định của WWDG

+ WDGTB[1:0] quyết định giá trị chia của bộ chia tần WWDG.

– Dao động của WWDG là APB1 clock, bắt nguồn từ nguồn dao động chính của vi điều khiển và được chia cho 4096 trước khi đi qua bộ chia tần của WWDG. Bộ chia tần của WWDG được cấu hình bởi bit WDGTB[1:0] trong thanh ghi Congifuration (WWDG_CFR) với giá trị chia 1,2,4,8 tương ứng với các giá trị bit cài đặt 00, 01,10 và 11. Clock sau khi qua bộ chia của WWDG sẽ làm cho downcounter thực hiện việc đếm xuống.

– Early Wakeup Interrupt: Tính năng Early Wakeup Interrupt được cho phép sử dụng khi bật bit EWI trong thang ghi WWDG_CFR. EWI sẽ được kích hoạt khi giá trị downcounter bằng 0x40 (trước khi reset). EWI được sử dụng để thực thi một số lệnh, hoạt động an toàn nào đó hoặc để ghi log dữ liệu trước khi MCU bị reset. Trong nhiều trường hợp thì ISR sẽ reload lại WWDG counter để tránh WWDG reset khi ISR thực hiện 1 nhiệm vụ tốn nhiều thời gian. Cần lưu ý, một số lỗi làm cho ISR sẽ không được thực hiện như hệ thống đang bị kẹt trong 1 nhiệm vụ có ưu tiên cao.

II. Một số thanh ghi

– Thanh ghi Configuration register – WWDG_CFR

– Thanh ghi Control register – WWDG_CR

Bước 1: Kích chọn dòng STM32F411VETx và sau đó chọn “Start Project”.

Bước 2: Chọn Serial Wire để nạp code

Bước 3: Click chuột phải vào chân PD12 sau đó tích vào ô GPIO_Output

Bước 4: Click chọn ô Activated để sử dụng tính năng WWDG

Bước 5: Cấu hình các thông số WWDG

WWDG counter clock prescaler = 8

WWDG clock counter = (PCLK1 (16MHz)/4096)/8) =488.28 Hz (~2048 us)

WWDG Window value = 80 có nghĩa là bộ đếm WWDG chỉ nên được refresh khi bộ đếm dưới 80 và lớn hơn 64 (0x40), nếu không MCU sẽ bị reset.

WWDG Counter value = 127: bộ đếm WWDG được thiết lập giá trị ban đầu = 127

WWDG timeout = ~2048 us * 64 = 131 ms

Không được phép refresh trước 2048 us * (127 – 80) = 96.2 ms.

Bước 6: Kích hoạt ngắt WWDG (Early Wakeup)

Bước 7: Cấu hình Project ở mục Project Manager và sinh code

Bước 8: Code

Để thấy rõ tính năng WWDG ta cho chương trình nhấp nháy led PD12 trong khoảng thời gian t_delay với giá trị t_delay là do người dùng thiết lập, sau đó set lại giá trị WWDG Counter value.

– Nếu 92.6 (ms) < t_delay < 131 (ms), MCU reset lại WWDG Counter trong khoảng “Refresh allowed” vì vậy chương trình sẽ nhấp nháy led PD12 bình thường với thời gian = t_delay

– Nếu t_delay < 92.6 (ms), MCU reset lại WWDG Counter trong khoảng “Refresh not allowed” vì vậy MCU sẽ bị reset và led PD12 tắt.

– Nếu t_delay > 131 (ms), thời gian delay lúc này lớn hơn timeout vì vậy chương trình thực hiện hàm HAL_WWDG_EarlyWakeupCallback() và sáng led PD12.

|

1 2 3 4 5 6 7 |

/* USER CODE BEGIN 0 */ void HAL_WWDG_EarlyWakeupCallback(WWDG_HandleTypeDef *hwwdg) { WWDG->SR = 0x00; // Clear interrupt flag // Clear interrupt flag HAL_GPIO_WritePin(GPIOD, GPIO_PIN_12, GPIO_PIN_SET); } /* USER CODE END 0 */ |

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

/* USER CODE BEGIN 2 */ uint16_t t_delay = 100; //change t_delay = 100 or 90 or 140 /* USER CODE END 2 */ /* Infinite loop */ /* USER CODE BEGIN WHILE */ while (1) { /* USER CODE END WHILE */ /* USER CODE BEGIN 3 */ HAL_Delay(t_delay); HAL_WWDG_Refresh(&hwwdg); // Set WWDG Counter value again HAL_GPIO_TogglePin(GPIOD, GPIO_PIN_12); // To show that normal operation is OK } /* USER CODE END 3 */ |

Lần lượt thay đổi các giá trị t_delay = 100, 90 và 140 để thấy cách hoạt động của MCU ứng với 3 trường hợp ở trên.

Bước 9: Build và Load chương trình.

TAPIT ARM R&D